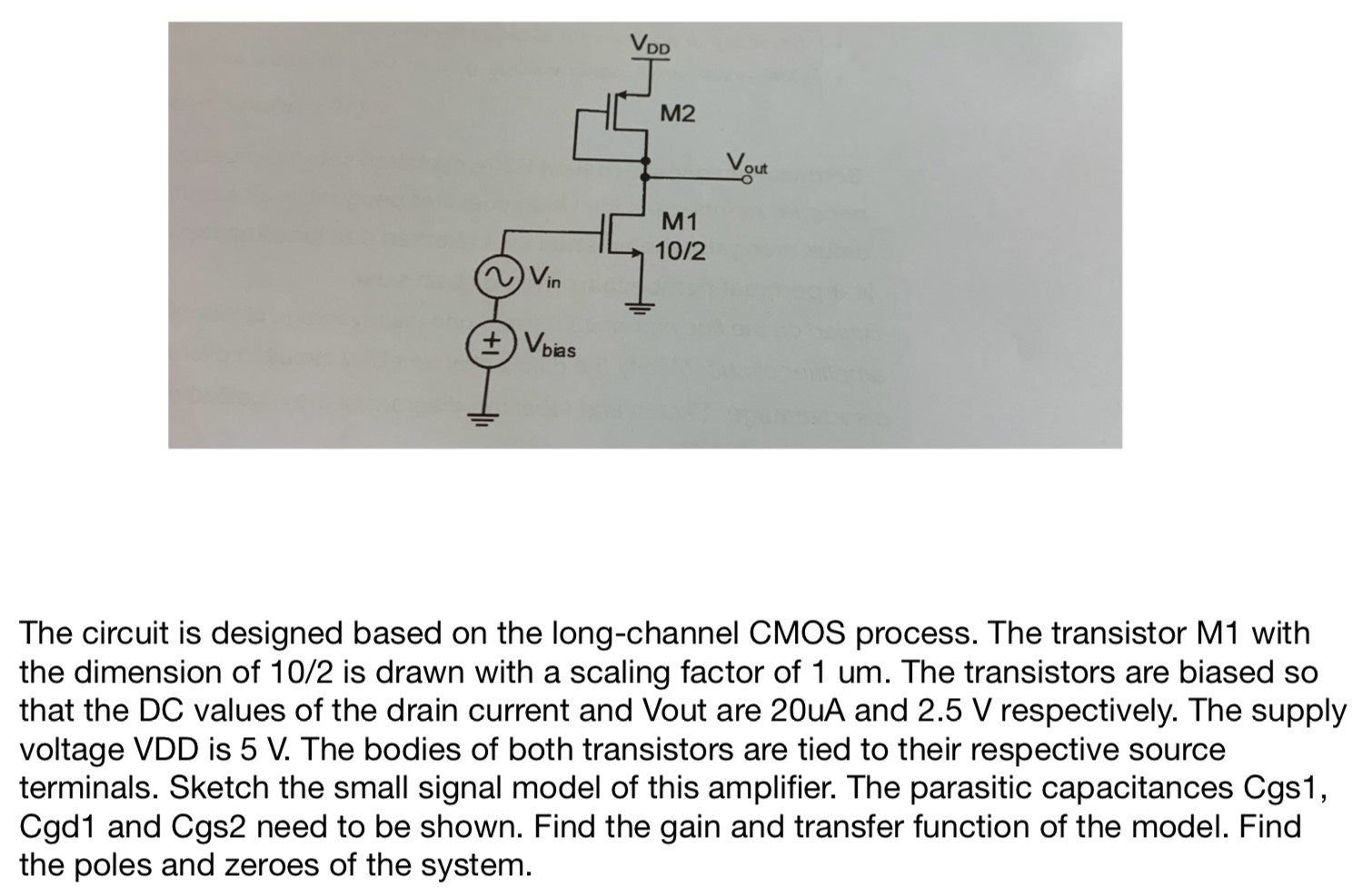

The circuit is designed based on the long-channel CMOS process. The transistor M1 with the dimension of 10/2 is drawn with a scaling factor of 1 um. The transistors are biased so that the DC values of the drain current and Vout are 20 uA and 2.5 V respectively. The supply voltage VDD is 5 V. The bodies of both transistors are tied to their respective source terminals. Sketch the small signal model of this amplifier. The parasitic capacitances Cgs1, Cgd1 and Cgs2 need to be shown. Find the gain and transfer function of the model. Find the poles and zeroes of the system.